隨著電力系統和工業自動化領域對設備可靠性、安全性要求的日益提高,高低壓開關柜、機箱機柜及配電柜的密封性能成為保障其長期穩定運行的關鍵因素之一。專業的密封條,尤其是針對柜體結構設計的U型密封條,在其中扮演著不可或缺的角色。當前,眾多廠家正推出促銷活動,旨在將高品質的密封解決方案更廣泛地服務于市場。本文將通過高清細節圖片,結合科技開發視角,深入解讀這類密封條的重要性與技術內涵。

一、 密封條的重要性:守護柜內“微環境”

高低壓開關柜、配電柜等設備內部集成了精密的電氣元件、控制模塊和連接線路。它們不僅需要防范外部塵埃、潮氣、腐蝕性氣體的侵入,以避免短路、氧化、絕緣性能下降等問題,還需在一定程度上隔絕噪音、震動,并在火災等緊急情況下起到一定的阻燃、延緩火勢作用。一條優質、貼合緊密的密封條,正是構建這一防護屏障的第一道也是極為關鍵的一道防線。U型結構的密封條,憑借其優異的卡扣貼合性和彈性恢復能力,能緊密包裹柜門邊緣,確保密封的持久有效。

二、 高清細節圖賞:透視產品工藝與品質

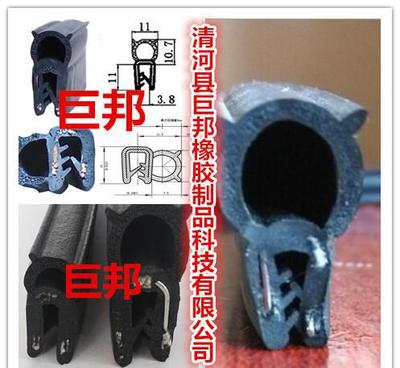

在廠家提供的促銷產品圖中,我們可以通過高清特寫觀察到密封條的諸多細節:

- 材質紋理:優質產品多采用硅橡膠、三元乙丙橡膠(EPDM)或氯丁橡膠等材料。高清圖能清晰展現材料表面的均勻度、光澤感以及可能的抗老化、抗紫外線添加劑痕跡。EPDM材質因其卓越的耐候性、耐溫性(-50°C至+150°C)和抗腐蝕能力,成為戶外及嚴苛環境下的首選。

- 結構設計:U型槽設計是亮點。細節圖可以清晰展示U型槽內部的空腔結構、加強筋(龍骨)設計以及內壁的防滑紋理。空腔結構提供良好的壓縮回彈性,確保門關閉時能均勻受壓密封;加強筋增強整體結構性,防止長期使用變形;防滑紋理則確保密封條能牢固卡在柜體鈑金邊緣,不易脫落。

- 截面與邊緣:高清圖能展現截面是否規整、邊緣是否光滑無毛刺。精密的模具和生產工藝是保證截面一致性、確保全長密封性能均勻的關鍵。光滑的邊緣避免安裝時劃傷柜體或操作人員,也提升了美觀度。

- 接角處理:對于需要拐角安裝的密封條,廠家通常會提供預成型接角或詳細的拼接指導。細節圖能展示接角處是否處理平滑、無縫,這是保證柜體角落密封無死角的重要環節。

三、 科技開發驅動下的密封條演進

高低壓開關柜的科技開發,同樣帶動了其配套密封技術的進步:

- 材料科學創新:研發更環保、更耐極端環境(如高寒、高熱、強化學腐蝕)、具有更長使用壽命(抗老化)的新型高分子復合材料。例如,部分高端密封條已集成導電纖維,兼具電磁屏蔽(EMI)功能,滿足精密電子機柜的需求。

- 智能化與集成化:在工業物聯網(IIoT)背景下,未來密封條或許能集成微傳感器,用于實時監測柜內壓力、濕度或密封條本身的受壓狀態、老化程度,實現預測性維護,將被動防護升級為主動監控。

- 定制化與模塊化設計:隨著開關柜設計的多樣化,密封條的開發也趨向于提供更多尺寸、硬度(邵氏硬度)、顏色選擇,并能根據客戶柜體的特殊結構進行快速定制。模塊化設計使得安裝、更換更為便捷。

- 仿真與測試技術:利用計算機流體動力學(CFD)仿真分析密封條在不同壓力、溫度下的形變與密封效果;通過嚴格的鹽霧測試、高低溫循環測試、壓縮永久變形測試等,確保產品在實際工況下的可靠性。

四、 選購與安裝建議

面對廠家的促銷活動,用戶在選購時不應僅關注價格,更應結合高清細節圖與廠家提供的技術參數(如材質、工作溫度范圍、防火等級、執行標準等)進行判斷。建議:

- 確認材質是否適合您的應用環境(室內、室外、特殊工業環境)。

- 測量準確尺寸,確保U型槽寬度與柜體鈑金厚度匹配。

- 關注安裝指導,確保清潔安裝面、從一角開始均勻按壓安裝、對接角進行妥善處理。

一張張清晰的高清細節圖,不僅展示了U型機箱機柜密封條、配電柜密封條的精密制造工藝,更揭示了其背后以科技開發為驅動的性能追求。在廠家促銷的契機下,選用一款高品質的密封條,是對高低壓開關柜等關鍵電力設備進行長效投資與智能化升級的重要一步。它雖是小部件,卻關乎整個系統運行的大安全與高效率。